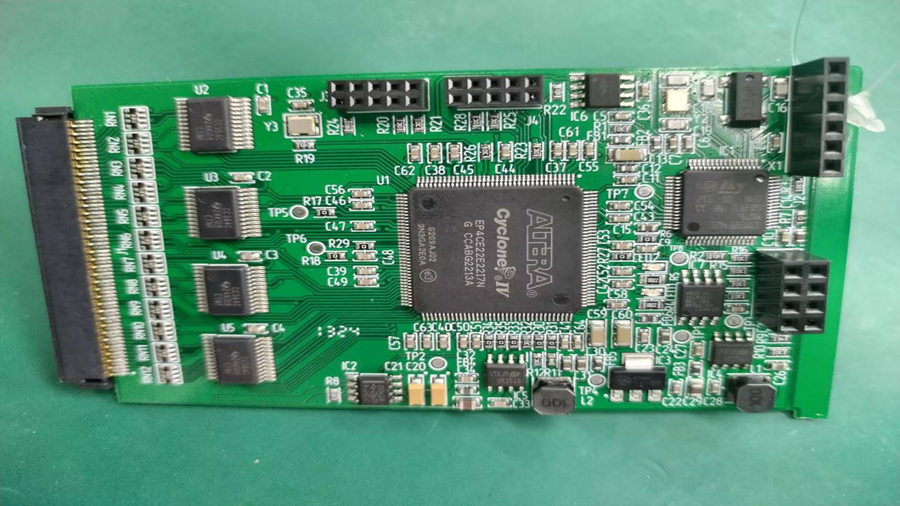

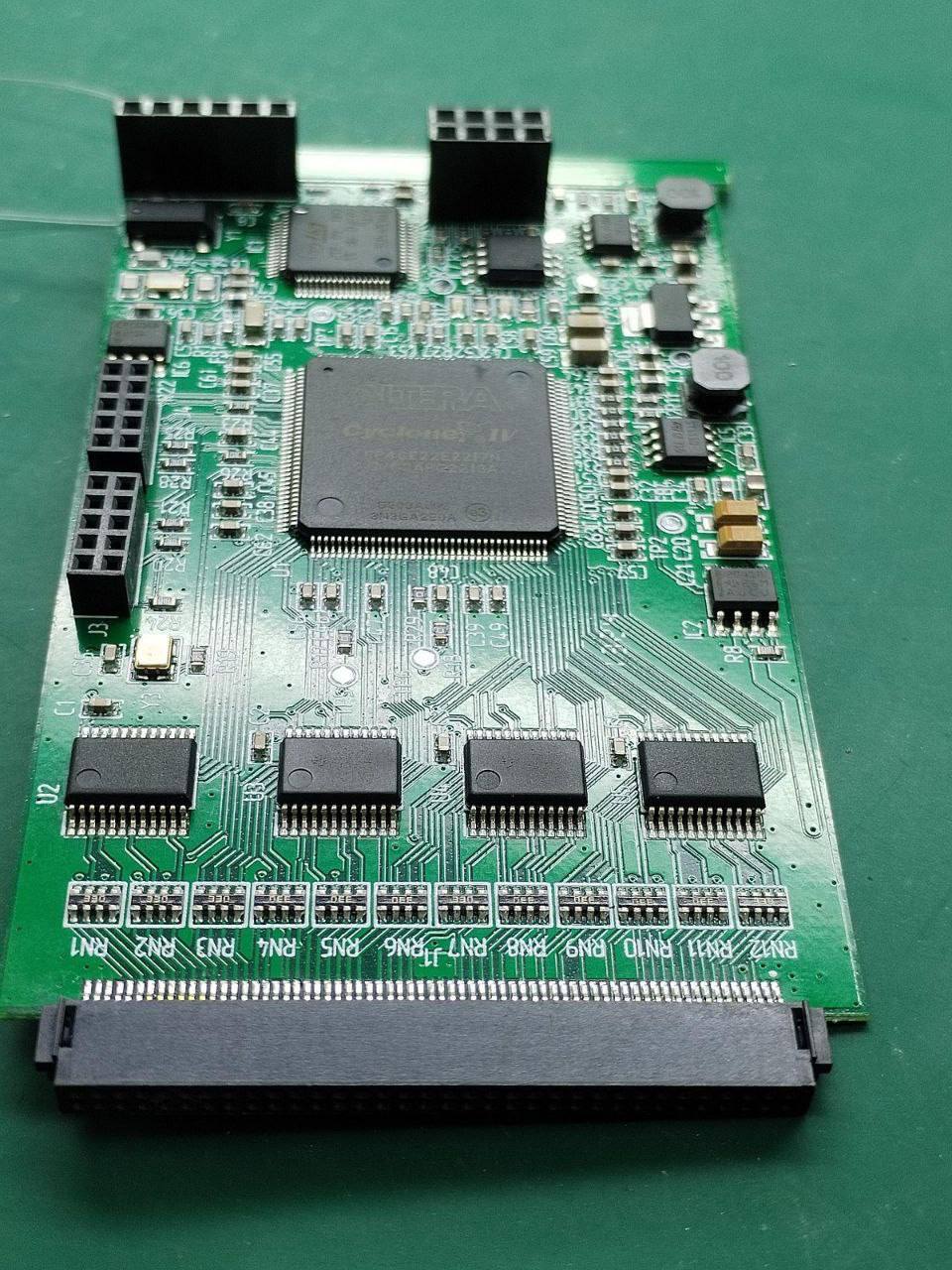

Development of the CAM Module

Project Goals

Create a CAM module compliant with international standards EN 50221 and ETSI TS 101 699. Ensure a flexible FPGA-based architecture with scalability for future expansion. Integrate with the CAS-RSCC system. Implement a complete processing cycle: from demultiplexing to decrypting the transport stream.

Technical Features

Hardware implementation on SOC architecture (FPGA) with ARM or RISC-V processor. Support for Trusted Execution Environment (TEE) to protect keys and data. Built-in support for RSA and SHA-256 algorithms. Firmware update capability via transport stream, including error protection and rollback mechanism.

Results

We paid special attention to security by implementing: Multi-level key protection, Support for digital broadcasting standards, Encryption compliant with GOST requirements, Reliable update and integrity control mechanisms.

Technical Features

Hardware implementation on SOC architecture (FPGA) with ARM or RISC-V processor. Support for Trusted Execution Environment (TEE) to protect keys and data. Built-in support for RSA and SHA-256 algorithms. Firmware update capability via transport stream, including error protection and rollback mechanism.